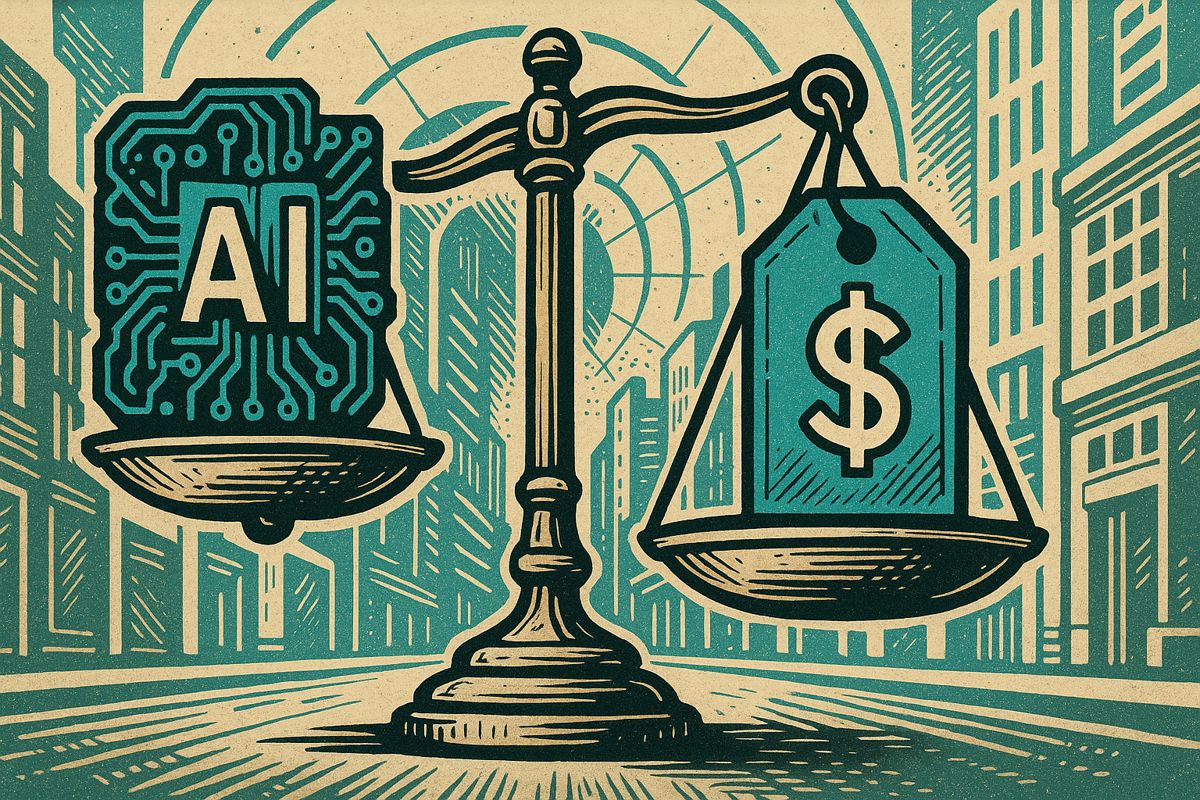

The era of unchecked AI spending is over. Firms are now turning to custom AI chips to cut workload costs by up to 60% and reduce power consumption by half. As CFOs demand clear ROI, a strategic convergence of specialized hardware, smarter software, and strict financial governance is reshaping AI infrastructure for maximum efficiency.

Hardware pivots that trim the bill

Custom AI chips achieve these savings by being tailored to specific tasks. Unlike general-purpose GPUs, they use optimized circuits and narrower data formats (like INT8) for inference workloads. This specialization dramatically lowers the cost per query and reduces the energy required for data movement and computation.

Specialized silicon is leading the charge in cost reduction. According to PwC, custom inference chips and edge accelerators can deliver a 40-60 percent lower cost per workload and cut power consumption by up to 50% compared to general-purpose GPUs. Data centers are also adopting hybrid CPU-GPU pipelines, a technique where model weights are stored in cheaper CPU memory, reserving expensive GPU resources for core mathematical operations. This approach, explored by USC Viterbi engineers, trims energy draw and lessens dependence on high-priced HBM.

Further gains come from shrinking process nodes. The move from 5nm to 3nm fabrication packs more transistors into the same space, boosting compute density. Innovations like TSMC’s AI-assisted yield optimization have reportedly increased 3nm output by 20%, directly lowering chip prices.

Software, algorithms and smarter spending

Gains from software and algorithmic efficiency are now rivaling those from hardware. The 2025 Stanford AI Index highlights that smarter model architectures contribute as much to performance as silicon advancements. Techniques like sparsity, 4-bit quantization, and retrieval-augmented generation (RAG) significantly cut inference latency while maintaining accuracy. Citing researchers at MIT FutureTech, these algorithmic tweaks alone have doubled training efficiency since 2023.

This focus on efficiency is also reshaping procurement strategies. While Gartner projects AI-optimized IaaS spending to double to $37.5 billion by 2026, competition is shifting. Vendors now compete on granular, value-based pricing (per-token or per-image) instead of raw GPU hours, with contracts increasingly tied to utilization and power consumption metrics.

Obstacles on the road to leaner AI

Despite these advances, many organizations struggle with fundamental challenges on the path to leaner AI. The 2025 State of AI Cost Management survey reveals that 80% of companies miss their AI cost forecasts by over 25%. Key obstacles include a lack of accurate cost metering, poor cross-team accountability, and difficulties integrating with legacy systems. A common pitfall is fragmented telemetry that obscures true GPU utilization, leading to massive inefficiencies.

In response, financial leaders are demanding real-time dashboards that translate technical metrics like FLOPs and kilowatt-hours into direct dollar costs. As analyst James Wang notes, resource scarcity historically drives innovation – a principle now forcing the AI industry toward sustainable growth.

Looking ahead

Looking ahead, the trend toward efficiency is set to accelerate. Inference, which already constitutes the majority of AI workloads, has seen its price plummet over 100-fold in two years. As specialized chips, optimized models, and granular financial controls become standard, the industry is transitioning from an era of exuberant spending to one where operational efficiency is the definitive competitive advantage.

How do custom AI chips cut workload costs by 60 percent and power by half?

PwC benchmarks show that replacing general-purpose GPUs with ASICs or edge-AI accelerators tailored to a single model shrinks per-query silicon area and memory traffic.

– 40-60% lower hardware cost per inference because the die contains only the logic the model actually calls.

– 50% better power efficiency thanks to fixed-function pipelines and narrower bit-widths (INT8 vs FP16), trimming data-center energy bills by 10-20%.

The result is a 60% drop in total workload cost and ≈50% reduction in power draw compared with running the same job on a vanilla GPU farm.

Why are inference prices falling faster than training prices?

Training is still GPU-heavy, but inference dominates 2025 data-center cycles and lives on custom silicon.

– Semiconductor Engineering records a >100× plunge in customer-facing inference prices in just two years.

– Causes: 3nm nodes give more transistors per watt, AI-driven fabs raise yields (TSMC +20% on 3nm) and AI-specific chips remove overhead that training-class GPUs carry.

Because inference is called millions of times after a model is trained, even a 1-cent saving per 1,000 tokens multiplies into huge opex relief.

Which engineering tricks squeeze more work out of the same chips?

Hybrid CPU-GPU scheduling is gaining ground.

– USC researchers offload data pre-processing and weight storage to cheaper CPU memory, freeing scarce GPU HBM for pure math.

– This lifts utilisation 29-33% and cuts energy per token by up to 25% without new hardware.

Add algorithmic tweaks (sparse attention, 8-bit quantisation) and the same wafer can deliver ≈3× more inferences per hour.

How fast is AI infrastructure spending growing despite cost-saving moves?

Gartner expects the total AI market to hit $2 trillion in 2026, up 36% y/y, but cost control is now a board-level issue.

– AI-optimised IaaS will more than double from $18bn (2025) to $37.5bn (2026) as buyers rent instead of build.

– Yet 84% of firms report margin erosion because they still forecast AI bills with spreadsheets; 80% miss their forecast by >25%.

Efficiency chips and dynamic-allocating software are therefore moving from “nice-to-have” to mandatory to keep the growth trajectory profitable.

What should procurement teams ask chip vendors right now?

- Can you license re-configurable ASICs that survive at least two model generations, avoiding six-month obsolescence?

- Show power-per-inference curves at my target latency, not peak TOPS.

- Share roadmaps for on-chip sparsity engines and 3nm/2nm shrink timelines; these deliver the next 20-30% energy cut.

- Offer pay-per-use firmware updates so efficiency gains arrive as software drops, not new tape-outs.

PwC warns that “betting against compute cost decline has always lost money”; locking in long-term GPU purchase orders today could leave you paying tomorrow’s “stranded-asset premium.”